Servers running Intel Xeon Scalable Family processors have six memory channels per processor and up to two DIMMs per channel. To maximize a server's memory bandwidth and overall performance, it is important to have a balanced memory configuration installed. When incorrectly configured, available memory bandwidth to the server is limited and overall performance can be greatly reduced.

Memory Interleaving

The Intel Xeon Scalable Family processor optimizes memory accesses by creating interleave sets across the memory controllers and memory channels. For each processor, there are two memory controllers. Each memory controller is then attached to three memory channels with up to two DIMMs per channel.

An interleaving set is created when memory channels have the same total memory capacities. If four memory channels have the same total memory capacity and are using identical DIMMs on two memory channels on each memory controller, a 4-way interleave set is created.

In each memory channel, another level of interleaving called "Memory Rank Interleaving" is possible. A DIMM can contain multiple memory ranks, which improves memory performance as the total number of ranks on a memory channel increases. The Intel Scalable Family Processors are optimized for two to four memory ranks per memory channel.

Guidelines for balanced memory configurations

For a balanced memory subsystem the following guidelines should be followed:

- All populated memory channels have the same total memory capacity and the same total number of ranks

- All memory controllers on a processor socket have the same configuration of DIMMs

- All processor sockets on the same physical server should have the same configuration of DIMMs.

Examples of balanced memory configurations

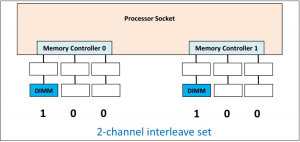

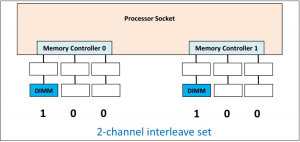

2-channel interleave set

This example consists of 2 DIMMs with both populated memory channels with the same memory capacity and the same configuration on each memory controller.

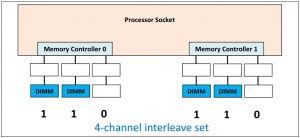

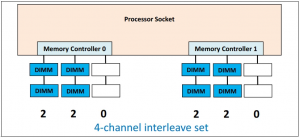

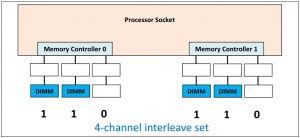

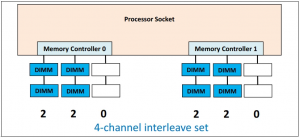

4-channel interleave set

This example consists of 4 DIMMs with four populated memory channels with the same memory capacity and the same configuration on each memory controller.

This example consists of 8 DIMMs with four populated memory channels with the same memory capacity and the same configuration on each memory controller.

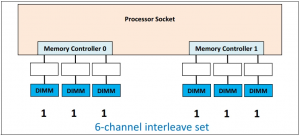

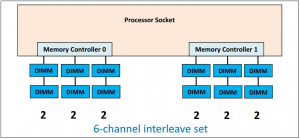

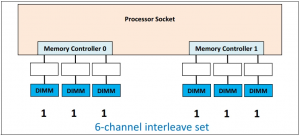

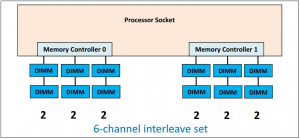

6-channel interleave sets

This example consists of 6 DIMMs with six populated memory channels with the same memory capacity and the same configuration on each memory controller.

This example consists of 12 DIMMs with six populated memory channels with the same memory capacity and the same configuration on each memory controller.

Balance Memory Guidelines for Intel Xeon Scalable Family Processors

Servers running Intel Xeon Scalable Family processors have six memory channels per processor and up to two DIMMs per channel. To maximize a server's memory bandwidth and overall performance, it is important to have a balanced memory configuration installed. When incorrectly configured, available memory bandwidth to the server is limited and overall performance can be greatly reduced.

Memory Interleaving

The Intel Xeon Scalable Family processor optimizes memory accesses by creating interleave sets across the memory controllers and memory channels. For each processor, there are two memory controllers. Each memory controller is then attached to three memory channels with up to two DIMMs per channel.

An interleaving set is created when memory channels have the same total memory capacities. If four memory channels have the same total memory capacity and are using identical DIMMs on two memory channels on each memory controller, a 4-way interleave set is created.

In each memory channel, another level of interleaving called "Memory Rank Interleaving" is possible. A DIMM can contain multiple memory ranks, which improves memory performance as the total number of ranks on a memory channel increases. The Intel Scalable Family Processors are optimized for two to four memory ranks per memory channel.

Guidelines for balanced memory configurations

For a balanced memory subsystem the following guidelines should be followed:

- All populated memory channels have the same total memory capacity and the same total number of ranks

- All memory controllers on a processor socket have the same configuration of DIMMs

- All processor sockets on the same physical server should have the same configuration of DIMMs.

Examples of balanced memory configurations

2-channel interleave set

This example consists of 2 DIMMs with both populated memory channels with the same memory capacity and the same configuration on each memory controller.

4-channel interleave set

This example consists of 4 DIMMs with four populated memory channels with the same memory capacity and the same configuration on each memory controller.

This example consists of 8 DIMMs with four populated memory channels with the same memory capacity and the same configuration on each memory controller.

6-channel interleave sets

This example consists of 6 DIMMs with six populated memory channels with the same memory capacity and the same configuration on each memory controller.

This example consists of 12 DIMMs with six populated memory channels with the same memory capacity and the same configuration on each memory controller.